Adders and subtractors are the building blocks that let digital circuits do math. They handle binary addition and subtraction, starting from simple single-bit operations and scaling up to multi-bit arithmetic used in real processors.

Understanding how these circuits work gives you a clear picture of how computers process numbers at the hardware level, and why design choices like carry propagation matter for speed.

Adders

Half Adder and Full Adder

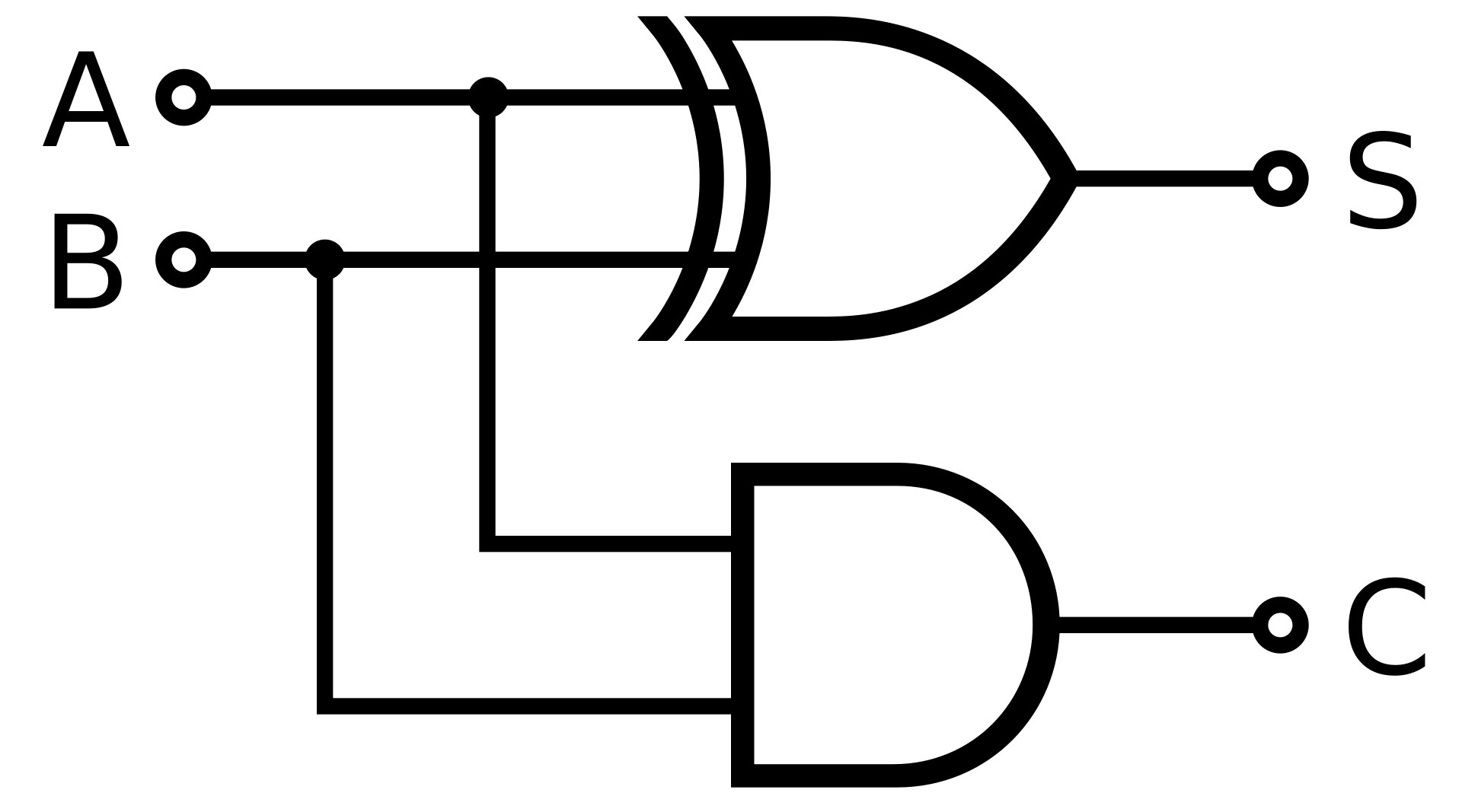

A half adder adds two single-bit binary numbers ( and ) and produces two outputs: a sum () and a carry out (). It uses an XOR gate for the sum and an AND gate for the carry.

The Boolean expressions are:

Think of it this way: the XOR tells you the single-bit result, and the AND tells you whether the addition "overflowed" into the next column (just like carrying a 1 in decimal addition).

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

The limitation of a half adder is that it has no input for a carry from a previous stage. That's where the full adder comes in.

A full adder adds three single-bit inputs: , , and a carry in (). It produces a sum () and a carry out (). Internally, you can build one from two half adders and an OR gate:

- The first half adder computes and .

- The second half adder adds to the result of the first XOR.

- The OR gate combines the two carry outputs to produce .

The Boolean expressions are:

| A | B | Cin | S | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Multi-bit Adders

To add numbers wider than one bit, you chain full adders together.

A ripple carry adder (RCA) is the simplest approach. You cascade full adders for an -bit addition, connecting the of each stage to the of the next. For example, a 4-bit RCA uses four full adders in series.

The downside is speed. Each full adder has to wait for the carry from the previous stage before it can produce a valid output. The total delay grows linearly with the number of bits, so a 32-bit RCA is roughly 32 times slower than a single full adder. This is called carry propagation delay.

A carry look-ahead adder (CLA) solves this problem by computing carry signals in parallel rather than waiting for them to ripple through. It uses two intermediate signals for each bit position:

- Generate (): a carry is produced at this stage regardless of the incoming carry.

- Propagate (): an incoming carry will pass through this stage.

Using these signals, the CLA calculates all carry bits simultaneously with dedicated logic. For instance, and , and so on. This is significantly faster than an RCA, but the trade-off is more complex hardware and more gates.

Subtractors

Half Subtractor and Full Subtractor

A half subtractor subtracts one single-bit number () from another (). It produces a difference () and a borrow out ().

- (same XOR as the half adder)

- (an AND gate with inverted)

The borrow output is 1 when and , because you need to "borrow" from the next column, just like borrowing in decimal subtraction.

| A | B | D | Bout |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

A full subtractor handles three inputs: , , and a borrow in () from a previous stage. It's built from two half subtractors and an OR gate, similar to how a full adder is built from half adders.

| A | B | Bin | D | Bout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

In practice, dedicated subtractor circuits are rarely built. Instead, most systems use an adder combined with two's complement to perform subtraction, which means the same hardware handles both operations.

Arithmetic and Overflow

Two's Complement Arithmetic

Two's complement is the standard way digital systems represent signed (positive and negative) integers. Positive numbers look the same as regular binary. To represent a negative number:

- Start with the binary representation of the positive value.

- Invert all the bits (flip 0s to 1s and 1s to 0s).

- Add 1 to the result.

For example, in an 8-bit system, is 00000101. To get : invert to get 11111010, then add 1 to get 11111011.

For bits, the representable range is to . So an 8-bit system covers to .

The big advantage of two's complement is that addition and subtraction use the same adder circuit. To subtract from , you just negate (invert and add 1) and then add it to . This is why most processors don't need separate subtractor hardware.

Overflow Detection

Overflow happens when the result of an arithmetic operation falls outside the representable range. In two's complement, this occurs when:

- Adding two positive numbers gives a negative result, or

- Adding two negative numbers gives a positive result.

Adding a positive number to a negative number can never overflow, because the result is always between the two operands.

The hardware detection method: compare the carry into the most significant bit (MSB) with the carry out of the MSB. If they differ, overflow has occurred. In Boolean terms, the overflow flag is:

For example, in a 4-bit system, adding (+7) and (+1) gives (-8), which is clearly wrong. The carry into bit 3 is 1 and the carry out of bit 3 is 0, so , flagging the overflow.

Detecting overflow matters because ignoring it leads to silently wrong results. Systems handle it in different ways: raising an exception, saturating to the max/min value, or setting a status flag for software to check.