Exception handling in pipelined processors is a crucial aspect of maintaining system stability and correctness. It involves detecting and managing unexpected events during instruction execution, ensuring the processor can recover gracefully and resume normal operation.

This topic explores the challenges of implementing precise exceptions in pipelined architectures, where multiple instructions are executed simultaneously. We'll examine various hardware and software mechanisms used to handle exceptions efficiently while minimizing performance impact.

Exception Types in Pipelines

Precise and Imprecise Exceptions

- Precise exceptions preserve processor state at the moment of detection, allowing the exception handler to resume execution from the same point after handling the exception

- Examples include illegal opcodes, division by zero (attempting to divide a number by zero), and page faults (accessing a memory page not currently loaded into main memory)

- Imprecise exceptions do not precisely preserve processor state at the moment of detection, making it difficult to resume execution from the same point

- Examples include floating-point exceptions (errors in floating-point arithmetic operations) and bus errors (issues with data transfer on the system bus)

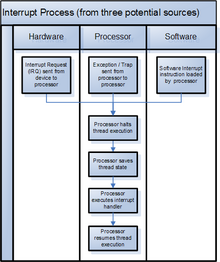

Interrupts

- Interrupts are exceptions triggered by external events, such as I/O requests (completion of data transfer from a peripheral device) or timer interrupts (periodic signals generated by a system timer)

- Interrupts are typically handled differently than exceptions, as they are not necessarily tied to a specific instruction

- Interrupt handlers are invoked based on the type of interrupt rather than the specific instruction that caused the exception

- Interrupts may require saving and restoring additional processor state, such as the program counter and status registers

Challenges of Exception Handling

Simultaneous Instruction Execution

- Multiple instructions are executed simultaneously in different pipeline stages, complicating exception handling

- When an exception occurs, the pipeline must be flushed, discarding all partially executed instructions and preserving the processor state at the point of the exception

- This process can be complex and time-consuming, especially for deep pipelines with many stages

- Out-of-order execution and speculative execution in advanced pipelined processors further complicate exception handling

- Processor state may not be consistent with the program order at the time of the exception, requiring additional tracking mechanisms

Precise Exception Handling Requirements

- Precise exception handling requires additional hardware mechanisms to track the state of each instruction in the pipeline

- Hardware must ensure that the processor can accurately restore the state upon exception detection

- This may involve storing intermediate results, register values, and memory addresses for each instruction

- Imprecise exceptions pose challenges in determining the exact instruction that caused the exception and the appropriate point to resume execution after handling the exception

- May require software intervention or complex hardware mechanisms to reconstruct the precise state

Exception Handling Mechanisms

Hardware Components

- Exception detection logic: Circuitry that monitors the pipeline for exceptional conditions and triggers an exception when detected

- Examples include comparators for detecting division by zero or invalid memory addresses

- Pipeline flushing: Mechanisms to discard partially executed instructions and restore the pipeline to a consistent state upon exception detection

- May involve invalidating pipeline registers, clearing buffers, and resetting control signals

- Precise exception tracking: Hardware structures that maintain the precise state of each instruction in the pipeline

- Examples include reorder buffers (ROB) that track the original program order of instructions and history buffers that store intermediate results and register values

- Exception vectors: Predefined memory locations that store the addresses of exception handlers for different types of exceptions

- Used to quickly jump to the appropriate handler when an exception occurs

Software Components

- Exception handlers: Routines that are invoked when an exception occurs, responsible for handling the exceptional condition and resuming normal execution

- Examples include division by zero handlers, page fault handlers, and interrupt service routines (ISRs)

- Operating system support: The operating system provides mechanisms for registering exception handlers, managing processor state during exceptions, and facilitating context switches if necessary

- This may involve maintaining exception tables, providing system calls for registering handlers, and handling privilege level changes

- Advanced techniques: Processors may employ techniques like exception deferral (allowing the pipeline to continue executing instructions speculatively until the exception is resolved) or exception speculation (predicting the outcome of exceptions to minimize pipeline stalls)

Performance Impact of Exceptions

Pipeline Disruption

- Exception handling disrupts the normal flow of instruction execution and requires additional cycles to resolve the exception

- When an exception occurs, the pipeline must be flushed, discarding all partially executed instructions

- This results in wasted cycles and reduced throughput, as the pipeline must be refilled with new instructions after the exception is handled

- The time required to handle an exception depends on factors such as the type of exception, the complexity of the exception handler, and the depth of the pipeline

- Longer exception handling times lead to greater performance degradation

Impact on Deep Pipelines and Advanced Techniques

- In deeply pipelined processors, the performance impact of exceptions can be more pronounced

- A larger number of instructions may need to be discarded, and the pipeline takes longer to refill and resume normal execution

- Out-of-order execution and speculative execution can exacerbate the performance impact of exceptions

- More instructions may need to be discarded, and the processor state may require more complex restoration mechanisms

- Techniques like exception deferral and exception speculation aim to mitigate the performance impact of exceptions

- Allow the pipeline to continue executing instructions speculatively until the exception is resolved, potentially reducing the number of wasted cycles

Frequency and Distribution of Exceptions

- The frequency and distribution of exceptions in a program can affect overall pipeline throughput

- Programs with a high frequency of exceptions or clustered exceptions may experience more significant performance degradation compared to programs with fewer or more evenly distributed exceptions

- Frequent exceptions lead to more pipeline flushes and wasted cycles

- Clustered exceptions may cause the pipeline to stall for longer periods, reducing overall throughput

- Optimizing exception handling in software, such as minimizing the use of exception-prone instructions or restructuring code to avoid exception hotspots, can help mitigate the performance impact of exceptions