Multicore systems face significant scalability challenges as core counts increase. Amdahl's Law, resource contention, and power constraints limit performance gains. Memory hierarchy design, cache coherence, and interconnect topologies also impact scalability.

To address these bottlenecks, techniques like data partitioning, load balancing, and synchronization optimization are employed. However, trade-offs between scalability, performance, and programmability must be carefully considered when designing and programming multicore systems.

Scalability Challenges in Multicore Systems

Amdahl's Law and Sequential Bottlenecks

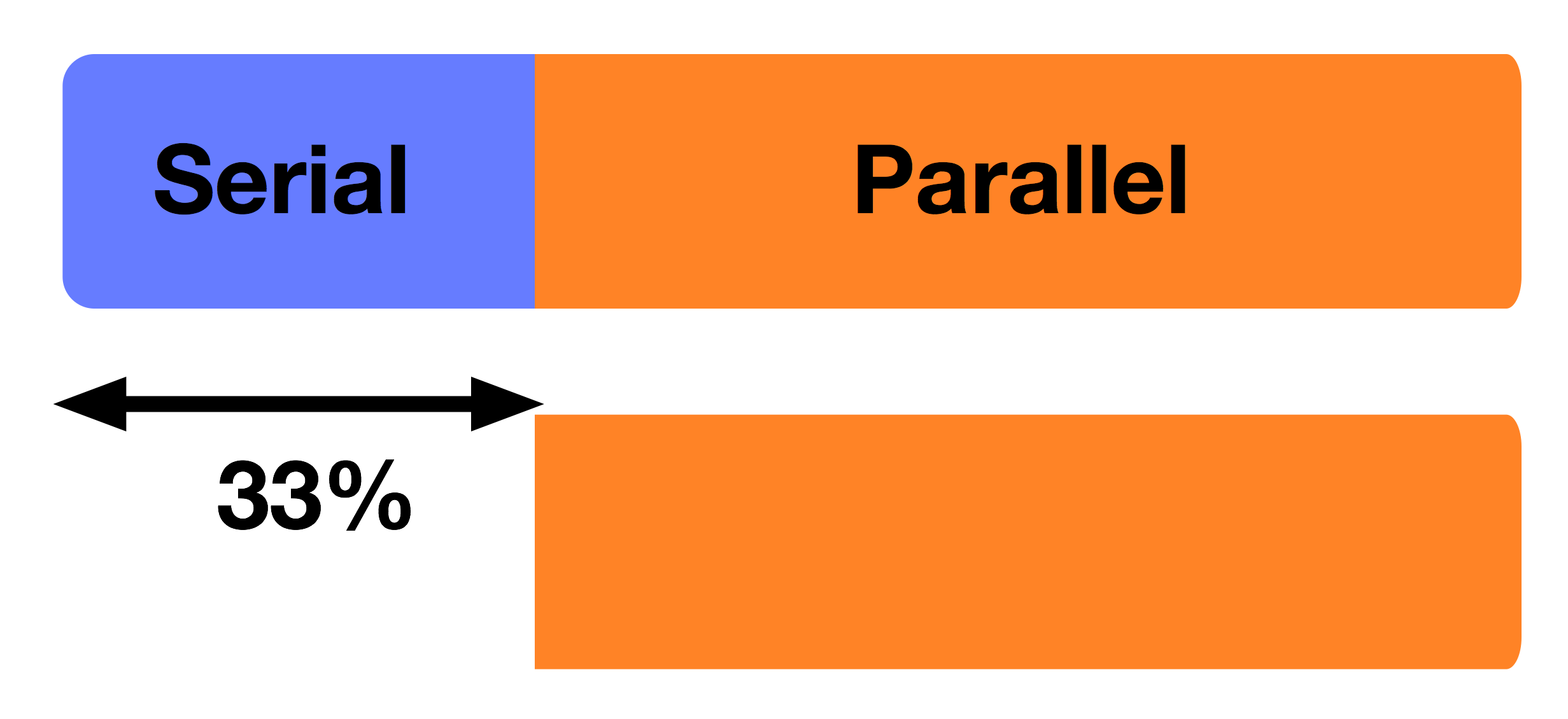

- Amdahl's law states that the speedup of a parallel program is limited by the sequential portion of the code, which becomes a significant bottleneck as the number of cores increases

- The sequential portion of the code does not benefit from additional cores and limits the overall speedup achievable through parallelization

- As the number of cores grows, the impact of the sequential bottleneck becomes more pronounced, limiting the scalability of the parallel program

- Example: If 10% of a program's execution time is sequential, the maximum speedup achievable with an infinite number of cores is limited to 10 times

Resource Contention and Synchronization Overhead

- Contention for shared resources, such as memory bandwidth and cache capacity, increases as the number of cores grows, leading to performance degradation and scalability limitations

- Cores compete for access to shared resources, resulting in increased latency and reduced throughput as the number of cores increases

- Synchronization overhead, such as lock contention and communication latency, becomes more pronounced with a higher core count, hindering scalability

- Locks are used to ensure exclusive access to shared data structures, but as the number of cores increases, the contention for locks intensifies, causing cores to spend more time waiting for locks instead of executing useful work

- Communication latency between cores increases with the number of cores, as data needs to be transferred across a larger interconnect network, adding overhead to parallel execution

Power, Thermal Constraints, and Diminishing Returns

- Power and thermal constraints limit the ability to increase clock frequencies, forcing designers to rely on increasing core counts for performance improvements, which exacerbates scalability challenges

- As the number of cores increases, the power consumption and heat generation of the processor also increase, requiring advanced power management techniques and cooling solutions

- Increasing clock frequencies to improve single-threaded performance becomes infeasible due to power and thermal limitations, making core count scaling the primary means of performance improvement

- Diminishing returns in performance are observed as the number of cores increases beyond a certain point, due to the limited parallelism available in many applications and the increasing overhead of managing parallel execution

- Applications may have limited inherent parallelism, meaning that adding more cores beyond a certain threshold does not provide significant performance gains

- The overhead of coordinating parallel execution, such as synchronization and communication, grows with the number of cores, offsetting the benefits of increased parallelism

Impact of Memory Hierarchy on Scalability

Memory Hierarchy Design and NUMA Architectures

- Memory hierarchy design, including cache sizes, associativity, and replacement policies, affects the ability of multicore systems to efficiently access and share data, impacting scalability

- Larger cache sizes can reduce the number of memory accesses and improve data sharing among cores, but they also increase access latency and power consumption

- Higher associativity in caches reduces conflict misses but increases the complexity and latency of cache lookups

- Replacement policies, such as least recently used (LRU) and pseudo-LRU, determine which cache lines are evicted when a new line is brought in, affecting cache performance and scalability

- Non-uniform memory access (NUMA) architectures, where memory access latencies vary depending on the location of the accessing core and the memory controller, can lead to performance bottlenecks and scalability issues if not properly managed

- In NUMA systems, cores have faster access to local memory compared to remote memory, requiring careful data placement and scheduling to minimize remote memory accesses and balance the workload across NUMA nodes

Cache Coherence Protocols and Overhead

- Cache coherence protocols, such as snooping and directory-based schemes, ensure data consistency across private and shared caches in multicore systems, but introduce overhead that can limit scalability

- Snooping protocols rely on a shared bus to broadcast cache coherence messages, which can become a bottleneck as the number of cores increases

- In snooping protocols, each cache controller monitors the shared bus for coherence messages and takes appropriate actions to maintain data consistency, leading to increased traffic and contention on the bus

- Directory-based protocols maintain a centralized or distributed directory to track cache line states and ownership, reducing the need for broadcasts but introducing additional latency and storage overhead

- The directory keeps track of which cores have copies of each cache line and their respective states (e.g., shared, exclusive, modified), enabling efficient coherence management

- However, the directory itself can become a scalability bottleneck, as it needs to be accessed and updated frequently, and its size grows with the number of cores and cache lines

Interconnect Topologies and Scalability

- Interconnect topologies, such as buses, crossbars, and networks-on-chip (NoCs), determine the communication latency and bandwidth between cores, caches, and memory controllers, affecting scalability

- Traditional bus-based interconnects become a bottleneck as the number of cores increases, due to the limited bandwidth and the need for arbitration to access the shared bus

- Crossbar interconnects provide dedicated communication paths between cores and memory, offering higher bandwidth and lower latency compared to buses, but they scale poorly due to the quadratic growth in the number of connections with the number of cores

- Hierarchical and scalable interconnect designs, such as mesh and ring networks, are employed to mitigate the limitations of traditional bus-based interconnects in large-scale multicore systems

- Mesh networks arrange cores and memory controllers in a grid-like topology, with each node connected to its neighboring nodes, enabling scalable communication but with potentially higher latency for distant nodes

- Ring networks connect cores and memory controllers in a circular topology, providing a balance between scalability and latency, but with limited bisection bandwidth compared to other topologies

Techniques for Addressing Scalability Bottlenecks

Data Partitioning and Locality Optimization

- Data partitioning involves dividing the input data and associated computations among cores to minimize shared resource contention and improve scalability

- Static partitioning techniques, such as block and cyclic distributions, assign data and tasks to cores at compile-time based on a fixed scheme

- Block distribution divides the data into contiguous chunks and assigns each chunk to a core, promoting spatial locality but potentially leading to load imbalance

- Cyclic distribution assigns data elements to cores in a round-robin fashion, providing better load balancing but potentially reducing spatial locality

- Dynamic partitioning techniques adapt the data distribution and task assignment at runtime based on factors such as core utilization, data locality, and communication patterns

- Dynamic partitioning can help balance the workload and optimize data locality based on the runtime behavior of the application, but it introduces additional overhead for monitoring and redistribution

- Data locality optimization techniques, such as cache-aware and cache-oblivious algorithms, aim to improve the spatial and temporal locality of data accesses to reduce cache misses and memory access latencies, thereby enhancing scalability

- Cache-aware algorithms explicitly consider the cache hierarchy and sizes to optimize data layout and access patterns, minimizing cache misses

- Cache-oblivious algorithms are designed to exhibit good locality properties regardless of the cache hierarchy, by recursively dividing the problem into smaller subproblems that fit into the cache

Load Balancing and Task Scheduling

- Load balancing aims to evenly distribute the workload across cores to maximize resource utilization and prevent performance bottlenecks caused by overloaded cores

- Work stealing is a dynamic load balancing technique where idle cores steal tasks from the queues of busy cores to balance the workload at runtime

- When a core becomes idle, it randomly selects another core and attempts to steal tasks from its queue, distributing the workload on-the-fly

- Task scheduling algorithms, such as work sharing and task-based parallelism, assign tasks to cores based on their availability and the dependencies between tasks to achieve load balancing

- Work sharing involves a centralized or distributed queue of tasks, where cores retrieve tasks from the queue as they become available, ensuring an even distribution of work

- Task-based parallelism expresses the program as a set of tasks with dependencies, and a runtime system schedules the tasks onto available cores based on their dependencies and core availability

Synchronization and Communication Optimization

- Synchronization and communication optimization techniques, such as fine-grained locking, lock-free data structures, and message aggregation, reduce the overhead associated with coordinating parallel execution and data sharing among cores

- Fine-grained locking involves using multiple locks to protect smaller regions of shared data, reducing contention and improving concurrency compared to coarse-grained locking

- Lock-free data structures, such as atomic operations and compare-and-swap (CAS) primitives, enable concurrent access to shared data without the need for explicit locks, minimizing synchronization overhead

- Message aggregation techniques, such as combining multiple small messages into larger ones, help reduce the number of inter-core communications and the associated latency and bandwidth overhead

- Hardware support for synchronization primitives, such as atomic instructions and hardware transactional memory (HTM), can further reduce synchronization overhead and improve scalability

Scalability vs Performance vs Programmability

Core Count and Complexity Trade-offs

- Increasing the number of cores can improve scalability and overall system performance, but it may also introduce additional complexity in software development and debugging, reducing programmability

- As the number of cores grows, the complexity of coordinating parallel execution, managing shared resources, and ensuring correctness increases, making it more challenging to develop and debug parallel programs

- Developers need to consider issues such as race conditions, deadlocks, and load balancing when writing parallel code for multicore systems, requiring additional expertise and effort

- Debugging parallel programs becomes more difficult as the number of cores increases, due to the potential for non-deterministic behavior and the need to reason about multiple execution paths simultaneously

Heterogeneous Architectures and Specialized Programming Models

- Heterogeneous multicore architectures, which combine cores with different performance characteristics and instruction set architectures (ISAs), can offer better performance and energy efficiency for specific workloads but may require specialized programming models and tools, impacting programmability

- Heterogeneous architectures may include a mix of high-performance cores, energy-efficient cores, and accelerators (e.g., GPUs, FPGAs) to cater to the diverse requirements of different application domains

- Programming for heterogeneous systems often requires the use of specialized programming models, such as OpenCL, CUDA, or OpenMP, which have a learning curve and may not be as intuitive as traditional sequential programming

- Developers need to explicitly manage the mapping of tasks to different types of cores, consider data transfer and synchronization between heterogeneous components, and optimize for the specific characteristics of each core type

Scalability-Performance-Programmability Trade-offs in Memory Systems

- Cache coherence protocols that prioritize scalability, such as directory-based schemes, may introduce additional latency and memory overhead compared to simpler snooping-based protocols, affecting performance

- Directory-based protocols provide scalability by reducing the need for broadcasts, but they require additional storage for the directory and introduce indirection latency for cache coherence operations

- Snooping protocols offer lower latency for cache coherence operations but limit scalability due to the increased traffic on the shared bus as the number of cores grows

- Scalable interconnect topologies, such as mesh and ring networks, may have higher latency and lower bandwidth compared to centralized crossbars, impacting the performance of latency-sensitive applications

- Mesh and ring networks provide scalability by distributing the communication load across multiple paths, but they may introduce higher latency for communication between distant nodes compared to a centralized crossbar

- Crossbars offer low-latency communication between cores and memory but scale poorly due to the quadratic growth in the number of connections with the number of cores

Trade-offs in Programming Models and Abstractions

- Programming models and languages that prioritize scalability and performance, such as message passing and actor-based models, may have a steeper learning curve and require more development effort compared to shared-memory programming paradigms, impacting programmability

- Message passing models, such as MPI, require explicit communication and synchronization between cores, which can be more complex and error-prone compared to shared-memory programming

- Actor-based models, such as Erlang and Akka, provide a higher-level abstraction for parallel programming based on lightweight threads and message passing, but they may require a different way of thinking about program design and decomposition

- Shared-memory programming models, such as OpenMP and Pthreads, offer a more intuitive and familiar programming experience but may not scale as well as message passing or actor-based models due to the challenges of managing shared data and synchronization

- Data partitioning and load balancing techniques that optimize for scalability may introduce additional runtime overhead and memory footprint, potentially affecting overall system performance

- Dynamic partitioning and load balancing techniques adapt to the runtime behavior of the application but introduce overhead for monitoring and redistribution of tasks and data

- Static partitioning and load balancing techniques have lower runtime overhead but may lead to suboptimal performance if the workload is not evenly distributed or if the application's behavior changes during execution